# Modified AES Optimization Strategies With Hierarchical Security For Internet-Of-Thing Applications

Rekha C<sup>1</sup>, Krishnamurthy G.N<sup>2</sup>

<sup>1</sup>BNM institute of Technology, Dept. of Computer Science and Engg, Bangalore.

<sup>2</sup>BNM institute of Technology, Dept. of Computer Science and Engg, Bangalore.

Abstract—Security in Internet of Things (IoT) plays a vital role in securing network and connected devices from IoT environment. Safe guarding security among internet enabled devices is a challenging task. The Advanced Encryption Standard (AES) for measurements encryption and verification. Be that as it may, those security capacities take a huge amount of handling power and quality/control consumption. In order to provide security to IoT Environment, the hierarchical level of security in an AES enabled IoT applications with modified optimization stratergies. The proposed work adopts security in a hierarchical way through power optimization, strength and better key sizes for key expansion and datapath. The outcome of the proposed work indicates the consistent energy utilization compared to existing AES methods. The proposed work even exhibits optimized power leakage and dynamic power.

**Index Terms**— Internet of Things(IoT), AES, Secutity.

## I. INTRODUCTION

The rise of the Internet of Things (IoT) paradigm brings the possibility of having any device related every time and everywhere. Such a heterogeneity and ubiquity increase some challenges and threats when in comparison with other more remoted and controlled communications. Nowadays, IoT devices are related to the Internet in numerous environments and fields such as industry or defense and public safety [1]. Nevertheless, safety troubles pose risks for human protection and privacy [2], and it may be stated that the broad adoption of IoT is slowed down because of privateness and safety necessities that have no longer been addressed absolutely [3]. The incorporation of physical objects with the Internet requires different correspondence models. This necessity will probably include some malignant models to the future Internet [4]. Security provisioning in an IoT system is a difficult assignment in light of the fact that each physical item has its own distinctive highlights. The personality of every individual, item and framework associated with the Internet should be confirmed. Without the personality check, the interlopers will access the system and perform different pernicious exercises. The outcomes of these exercises are various in nature with applications going from debilitating a home security framework, passing on false wellbeing readings to specialists to actuating false alarms. The answer for security and protection issues is to incorporate security highlights, for example, gadget recognizable proof, gadget/client confirmation, and information encryption. These protection capacities are regularly based on the cryptographic calculations, including open key cryptography and symmetric cryptography, which contain handling pressure and increment strength and power utilization. Conversely, IoT gadgets should be compelled minimal effort gadgets with constrained

preparing power, restricted memory impression, and even constrained power/vitality spending limit, for instance, control reaping gadgets and battery based gadgets. This prompts the significance of improving cryptographic calculations in equipment for cost, throughput, what's more, particularly power and vitality utilization. Be that as it may, cost, throughput, and power/vitality utilization are various highlights which are difficult to accomplish simultaneously. In this paper, we centered on the optimization techniques for 32-bit datapath structure to attain low-electricity, low-electricity excessive-throughput modified AES encryption module supplying hierarchical level of protection with a small region footprint. The region is stored using reorganizing the encryption datapath to reduce the extensive kind of information registers and combinations. Power and energy consumption is reduced by way of minimize activities in the datapath and inside the key enlargement; and via applying a clock gating approach to facts and key garage registers. Because of the 32bit datapath structure, the throughput in our gadget is at least 4 times more than the one of the exceptional 8bit datapath on the same frequency. With a couple of optimizations and by way of using FDSOI 28-nm generation, we can acquire very high throughput (approximately 28 Mb/s at 10 MHz) with a couple of levels of security at extremely low energy (less than 20 W at 0.6 V, 50 C with FDSOI 28-nm technology) and severe low strength in step with a bit (less than 1 pJ/b). This suggests that our AES 32- bit datapath architecture may be used for ultralow-strength IoT applications with a couple of diplomas of safety. In evaluation with the light-weight block cipher PRESENT in 128-bit protection mode inside the equal era node, our proposed a shape can gain the identical strength in keeping with a bit as the handiest of PROPOSED on everyday occasions.

The rest of this paper is arranged as follows. Section II in brief evaluations studies associated with this subject matter and Section III describes the proposed paintings using an optimization approach for a key increase. In Section IV, the simulation consequences and validation are tested. Finally, Section VI offers a paper end and destiny artwork.

## II. RELATED WORKS

The present issues on safety of the IoTs is robably explained with the aid of utilizing the cutting-edge available cryptographic natives strategies. Gadgets furthermore, conventions with legitimate use of recognizable proof, validation, furthermore, information encryption will lessen the danger of uncovering individual information to attackers. These cryptographic natives contain two fundamental classifications: symmetric cryptography and asymmetric cryptography (or then again open key cryptography).

Symmetric cryptography including square figure furthermore, stream figure is adjusted to information encryption in view of its quick tasks (generally XOR and stages). Between sorts of symmetric cryptography calculations, move figures are prepared for generating the scrambled information movement brief, be that as it could, they are confined to simply move statistics encryption. Interestingly, Asymmetric cryptography is increasingly adaptable in the application perspective, however it takes all the more preparing force, more information capacity, and significantly more power utilization notwithstanding when the cryptography modules are actualized in equipment.

There are numerous systems proposed as new adjustments for LEACH to give greater security and lessen vitality utilization. S-LEACH [5] uses building hinders from SPINS; a suite of exceptionally upgraded security building hinders that depend exclusively on symmetric-key techniques. SecLEACH [6] indicates how to contribute the key redistribution plan to verify hub to-CH correspondences. The principle thought is to produce an enormous pool of keys and their IDs at the time the system is sent, and at that point every hub

is doled out a gathering of these keys haphazardly. Additionally, every hub is alloted a pairwise key which it imparts to the BS.

The requirement for continuous cryptographic arrangements has moreover been communicated. In [7] the creators propose a continuous based AE conspire where the "constant key stream" is created from any protected square figure like AES. The creators present two methods of activity: the honesty mindful ongoing based counter (IAR-CTR) and the figure input (IARCFB) mode. Both the proposed methods of activity plan to offer both classification and message honesty in a solitary go without a tag. As indicated by the creators, their real-time arrangements are adjusted to frameworks where parameters like honesty mindfulness, dormancy, jitter, and parallelism are basic.

The symmetric figure calculations utilized in the validated encryption plan are AES and Present. In the two cases the fundamental structure objective is territory decrease, utilizing a key size of 128 bits. AES was chosen for being an outstanding broadly useful standard while Present was chosen as the lightweight figure to be utilized dependent on the outcomes announced in the writing about its exhibition and execution size [8].

Eschenauer and Gligor give a plan that can accomplish security furthermore, solid confirmation for the system quickly on organization [9]. This plan depends on Blom's plan. In any case, this plan does not ensure that any two neighbors can impart straightforwardly with one another. Correspondence between neighbors may take a long course. As hubs pass on, the system can without much of a stretch become detached. In a various leveled steering engineering, this plan isn't a viable answer for the key administration issue.

The IEEE 802.15.4/ZigBee is intended for a minimal effort, standard-based and adaptable remote system innovation, which offers low control utilization, dependability, interoperability and security for control and checking applications. ZigBee supports Advanced Encryption Standard (AES) encryption with a 128 bits key and information honesty utilizing a MAC. Notwithstanding, essential security components have a few vulnerabilities. TinySec is vulnerable to physical assaults [10]. Recently, there was the development of a new block cipher calculations which are lightweight as a ways as system or programming usage and memory impressions but they arrive up with diminished security levels, for example, PRESENT [11] have little equipment usage region in any case, utilize more encryption rounds and littler square estimates which prompts lower throughput. More seriously, these lightweight calculations are not embraced inside the new IoT proposition yet as a result of the absence of their examinations as some distance as protection and conventions. AES is still proper now chosen as the number one crude for security tool inside the growing proposition focusing on IoT applications.

Shankar and Eswaran [12] Proposed Visual Cryptography (VC) as a technique that secures a mystery image, in which the photo is encoded into various offers and administered to diverse individuals. In the offer creation process, the creators

showed a new condition for discretionary structures after which XOR exercises were performed to create 'n' transparencies. In 2015, Bhadravati et al. [13] suggested a Scalable Mystery Image Sharing (SSIS) strategy that outfitted moderate amusement with smooth versatilitly. In addition, this system was extended to chronicles and an adaptable mystery video sharing (SSVS) strategy was proposed. These two strategies are proposed to pack sight and sound. An epic PSO for dynamic WSN in MOP animate data move in frameworks and decline vitality misfortunes by El-Shorbagy et al. [14]. All things considered, in DMOPs, the upgrade time allotment is broken into a couple of comparable subperiods. Enemy models are important to the structure of demonstrated and secure cryptographic ,plans or conventions as opined by Do et al. in 2018 [15]. The characterization plan for fundamental application-based adversaries used the steady security and the key

papers were delegated per the proposed arrangement. Finally, the progressing work analyzes the models in the contemporary research field of IoT. Wavelet-based mystery picture sharing arrangement was proposed with encoded shadow pictures using perfect Homomorphic Encryption (HE) framework. From the outset, Discrete Wavelet Transform (DWT) was associated by Shankar et al. [16] to the mystery picture to make subbands. The scrambled shadow can be recovered by simply picking a few subsets of these 'n' shadows that makes it direct and stack more than each other. To improve shadow security, each shadow was encoded and unscrambled using the HE method. Regarding stresses with respect to quality, another Opposition-based Harmony Search (OHS) calculation was utilized to make the ideal key [17].

## III. PROPOSED METHOD

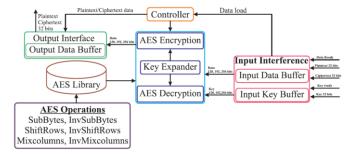

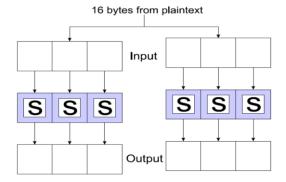

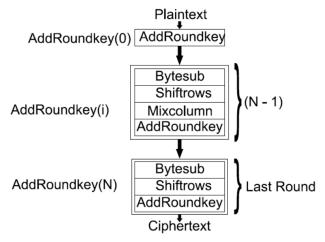

The block diagram of proposed system of 128-bits. Firstly it takes four 32-bits word length from the plaintext and four 32-bits word length from the cipher keys. Then the encryption/decruption is done on the data and the output is generated of length four 32-bits. The AES is composed of six additives as shown in Fig. 1 which each phase is related to each other. Input interference that's used to load the blocks of plaintext and to save input blocks which are looking ahead to encryption/decryption. The plaintext and the keys each are of 32-bit period and the output is of period 128-bits. Controller which acts as a nation controller that generates manage alerts for all different units within the gadget. AES Round is a Special component that's used to perforn the encryption/decryption of the enter facts using keys. Key Expanders computes all sets of internal cipher keys relies upon on a single external keys. Output Interfaces which collects the 128-bit duration data and fragments it into 4 32-bits phrase duration in a similar ways as Input key Buffer and Input Data Buffer for the enter. AES Library plays the sequential AES capabilities which are subBytes, shiftRows, Mixcolumns, AddRound keys, Inverse subBytes, Inverse shiftRows and Inverse MixColumns are described inside the library. The Bytesub transformation flow can be seen in Fig. 2. The encryption technique consists of several steps as shown with the aid of Fig. 3. After an initial addroundkey, a spherical characteristic is accomplished to the data block (which consist of bytesub, shiftrows, mixcolumns, and addroundkey transformation, respectively). It is completed iteratively (N instances) depending on the key period. The decryption form has exactly the identical series of versions just like the only within the encryption shape. The versions Inv-Bytesub, the Inv-Shiftrows, the Inv-Mixcolumns, and the Addroundkey permit the form of the vital component schedules to be identical for encryption and decryption.

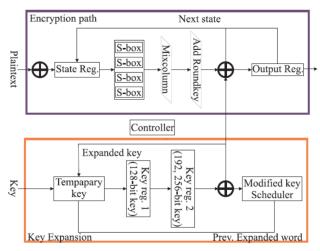

# A. AES Datapath Optimization

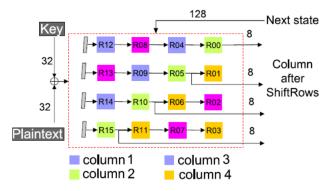

The AES optimization method as a key expansion algorithm, it has been used in many application. In the AES techniques shift registers utilized to easy the loading keys steps and statistics. By the usage of shift operations, both plaintext and key of 32-bit are loaded into the kingdom register and the important thing signs up at the equal time. By reducing the use of flip-flops, we additionally stored the amount of clock buffers and the power consumed through the clock tree due to the fact the clock tree from the clock buffer consumes a massive quantity of strength. To a further optimization the proper selection of S-box which consume minimal power dissipation as shown in Fig. 4. It reviews the set-up of Our proposed state check in. The prepared work check in is used so that once loading the plaintext and the input key, through transferring the block of 32- bit in each cycle the encryption is obtained. State check in contain sixteen 8-bit registers (which forms a "Matrix state") later segrigated into four number 4-stage shift registers. The AES standard specifies operations on rows and columns that shiftRow performs permutation operation for the rows in the state matrix, and for column the MixColumn operation is performed. But from the proposed design from the

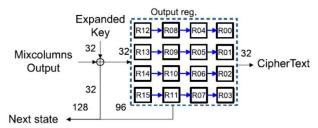

ShiftRow specification we totally removed the ShiftRows via selecting the diagonal from the state matrix(from top-left nook to bottom-proper nook). The effects from the nation sign in after performing every shift operation to the one column of the kingdom matrix after the ShiftRows. This operation minimizes the use of manage logics for the country registers, and vanishes the common sense for the ShiftRows steps. From our datapath, in serialising with the 8-bit block phase, Mix- Column is constructed as clean combinational logics which minimizes the percentage use of flip-flops. The state register's gets updated after every next state data generated where it ontents the output register is added with last 4 bytes from the round operation after every its four cycles as described in 6. According to the described details, we saved 32-bit register because the storing size of the temporary statistics for the encryption segment for the output register is handiest 4 \* 4- bits. The ultimate 32-bit records are ship again immediately to the state sign in. The output sign up is of form 4 \* 4-degree shift sign in which saves power and the computational region.

The 4 S-box which placed in among the kingdom check in and the output sign in. The MixColumns which triggers processing four-bit in every clock cycle. The output register contains the temporary results. When the processor finishes its encryption, results are optained from the output register. For the 128-bit key configuration, AES encryption section calls for 10 rounds, which of 40 cycles to finish the encryption of 128-bit block data. Our Proposed work uses total off 44 cycles to encryp a same data block. FOr remaining key configuration in AES it requires 52 and 60 cycles to encrypt 192 and 256-bit key data block, respectively. For kingdom sign up and the output register we use clock gating approach one at a time intern it saves the dynamic electricity intake. For instance, to shop strength inside the information loading nation, the clock for the output register is disable as it has no legitimate records for the output check in. When the device is in inactive state, the valves of the output registers isn't changed, which represents no activities present in the encryption phase. Even in the higher throughput mode the power estimation values shows that(44 cycles/encryption for 128-bit key length) from the applied clock gating process system can save more than 15% of power ratio. If the throughput valves decrease from the clock gating techniqur system can save higher power consumption.

## **B. State Tranformation**

The S-box in AES design has a excessive impact on place and the electricity consumption. By the proposed work, we chosen nice S-box to put in force for the intake of low power. The S-field will acquire the place up to 60% inside the total cellular location, and the consumption of electricity is 10% to 20% from overall strength used. Can proper is an S-container which demonstrates optimized place(294 gates/Scontainer) which uses greater electricity consumption because S-container includes extra sports specifically with 8 S-packing containers. The LUT-based S-field is most populated and directly forward S-field implementation. Sequentially LUTbased S-box is larger in area(434 gates/S-box) however the strength intake is lesser than the Can right S-box.

Fig. 1. Proposed Architecture

DES S-field is diagnosed as the most efficient S-field in power consumption, however it occupies a bigger area. DES S-field makes use of structure proposed for optimizing energy intake which defined in Fig. ??. The use of one hot decoder which converts S-box inputs to its one hot instance values. For the nonlinear operations wire permutation is used for its light weight cryptography algorithm. Later, the S-box result from onehot encoder is converted back to its original field size. DES S-box is used in proposed system because it involves minimal activities in the S-boc circuit which intern reduces power consumption. After the decryption phase, any one signal modifications its value to get input into the encoding country. DES S-box occupies extra space due to the encoder and decoder circuits size. This optimization consequences to 10% in electricity reduction in whole device. In proposed device DES S-box has the dimensions of 466 GEs/s-field with the 8% boom in size with assessment with LUT-based totally S-box. As a result, The S-boxes in our paintings consume simplest 10% of general energy consumed in the machine.

Fig. 2. Block diagrams for Substitution.

Fig. 3. AES algorithm- Encryption Structure

Fig. 4. Modified AES architecture

Fig. 5. Proposed state register

# C. AES Key Expansion

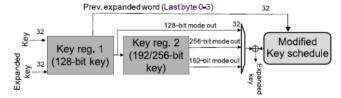

The shape of key growth which of two registers is presented in Fig. ??. The creation of key expansion makes use of identical mechanism as the encryption route for optimizations of S-boxes and the loading data to the important thing registers of various key sizes. To save the dynamic power consumption in S-box the inputs of S-boxes are master by means of a few constant values while key enlargement no longer used. The length of extended key is calculated and cargo returned immediately to the system key registers to store area. The key growth module achieve 4 \* 4- state shift registers, and a key remodel module, that have 4 S-boxes, and XOR.

Fig. 6. Proposed output register.

Fig. 7. Proposed Flow-chart of optimized Key Scheduling Algorithm.

For 128-bit key size, only certain shift registers are used, and for the clock sign the final shift registers is disabled for energy save. For 192-bit key length, the very first sign up and a decrease 1/2 of the second shift registers are used, for 256-bit key length, whole shift registers are used. The end result of the key expansion is despatched returned to the first key check in for maintains generation of the round keys.

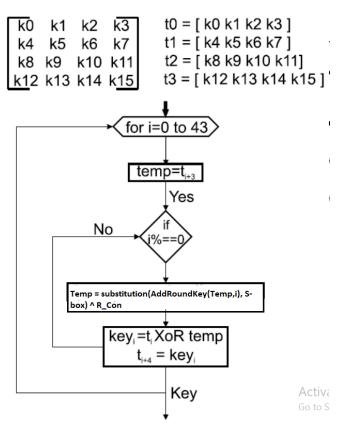

A modified key expansion algorithm 1. the key expanding upon of 4 \*4 matrix, as shown above matrix key, where 24-bit shift register are used for the process which from the key size, we use the alternative approach where the block is converted using AddRoundKeyWord, SubstituteWord, and XOR with RCON and a round steady. For 128-bit key length, all of the operations are carried out to the ultimate block after each 4 clock cycles, further for 192-bit key size and 256-bit key length, they're used each 4 and 8 clock cycles, respectively. For the 256-key length it calls for additional SubstituteWord inside the center of 8 clock cycles.

Fig. 8. Key registers.

```

Algorithm 1 Key Expansion Algorithm

1: procedure Key_Expansion(K, s_box)

2: t(0) = [K0K1K2K3];

3: t(1) = [K4K5K6K7];

4: t(2) = [K8K9K10K11];

5: t(3) = [K12K13K14K15];

6: for i=0 to 43 do

7: temp = t(i-1);

8: if i%4 == 0 then

9: temp = substitution(AddRoundKey(t, i),S_box) ^ R_Con

10: end if

11: key(i) = temp ^ t(i);

12: t(i+4) = key(i);

13: end for

14: end procedure

```

# Algorithm 2 AddRoundKey

```

1: procedure AddRoundKey(t,i)

2: shift = 0;

3: for j=i to i+3 do

4: t(j) = t(j) >> shift;

5: a(0) = t(j)&0x000000ff;

6: shift = shift +8;

7: end for

8: end procedure

```

Initially the temporal register stores the early rows elements as shown in Fig. 7. The temporal register comes with 44 rounds and from each round now key is generated which is highly secured. The temporal register is obtained using function, where is substituted using AddRondkey(temp) instead of rotation function as shown in the algorithm 2, Substitute Word, and XOR with RCON. Later the temp is XOR with tempi where i is from 0 to 44. Later the key is added to temporal register.

The input to the AddRoundKey function is 't' array and index i. depending on the value of index i, from t, the function considered diagonal element and returns 32 bit value. For example:

For i = 0,

The value return from the AddRoundKey function is [K3K6K9K12]. For i = 1,

The value return from the AddRoundKey function is [K7K10K13EK0]. Similarly for the rest of the values. The 32-bit key expansion's output is sent to the encryption path and perform XOR in the AddRoundKey stage. The clock gating is used in the key expansion to save power consumption. When system in idel state, there will be no activities in the key refister and the S-boxes.

#### IV. PERFORMANCE ANALYSIS

Our proposed model is a lightweight cryptography algorithm which PROPOSED and it modeled in VHDL, for synthesizes it uses Synopses DC Compiler, and a completely applied with Dependance divided for the SNACk of test chips the usage of ST FDSOI of 30-nm era. When the frequency is ready at 60 MHz to maximize target and it presents throughput of one hundred seventy and 120 Mb/s to its modifief AES encryption center and inside the proposed encryption core, respectively. The modified AES technique and the proposed encryption the module are concatenated to the cipher module to the test chip for the comparison. The electricity consumed for the machine at exclusive point is calculated with post log off extraction. The preciding sections increase the strength estimated for the effects to the SNACk chip and the security evaluation that the system is implemented the usage of the Synopses Prime Time Power,

# A. Experimental Configrations

The user interface from the encryption module in the SNACk chip are used shown in Fig. ??. It consists of the test environment for the proposed AES encryption model and it additionally makes use of a light-weight cryptography algorithm PROPOSED for the evaluation. The 32-bit statistics block interface with the important possibility of selecting extraordinary key sizes and for the cipher type between AES encryption middle and the PROPOSED encryption core. AES encryption center meant helps all of the encryption modes targeted with the activity of the AES standard which includes 128-bit, 192- bit, and 256-bit key length. The PROPOSED encryption middle together with the equal interface which incorporates modes: 80- bit and 128-bit keys. Both designshad been carried out using the identical phases.

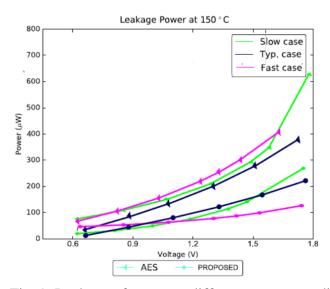

Fig. 9. Leakage of power at different corners vs different supply voltages.

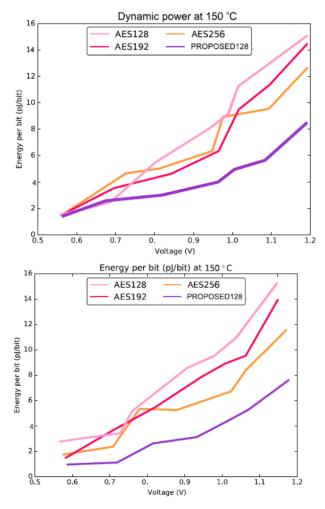

Fig. 10. Dynamic power usage during the supply at different voltages.

The take a look at surroundings for the block cipher module in SNACk chip are used. The plaintext and the key are loaded from the host cease via SPI interface. Inside the SNACk chip, a presence of SPI decoder with

APB-like interface which writes the take a look at information to the appropriate memories which incorporates the configuration registers, the plaintext reminiscence, the key reminiscence and the reference reminiscence. After loading of all required information, by using activating the contrl finite state machine the encryption take a look at is finished. If the encryption section is finished efficiently, then the walking sign is toggle. Until the manipulate finite state gadget receives the stop sign thru the SPI interface the encryption manner constantly going for walks repeatedly. Using this test configuration all the power estimation results for the next section is obtained.

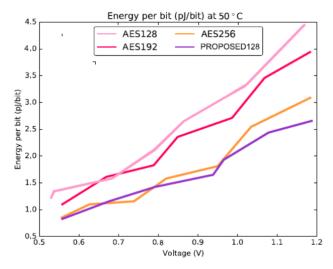

Fig. 11. Energy per bit of our AES implementation at typical corner at different working temperatures

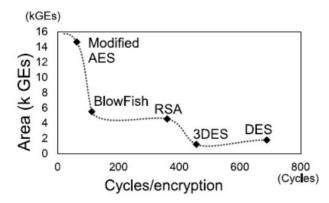

# Area (kGEs) vs. Cycles/encryption

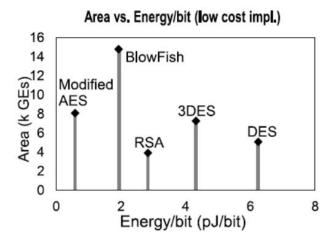

Fig. 12. Comparison with other low-cost AES implementations

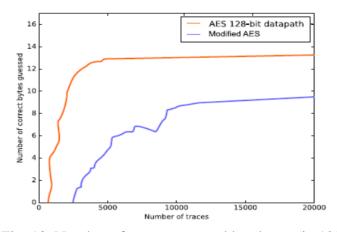

Fig. 13. Number of correct guessed key bytes (in 128-b key mode) by last round CPA attack.

## **B. Power-Estimation Results**

From the test environment in SNACk chip, we can test two encryption cores which having different key lengths for the different supply voltages and for different operating frequencies. The same plaintexts and the keys were push to all the encryption module. From the whole encryption module the activity of required post

signoff timing simulation is captured after every encryption module. By the generated results the worst case of power consumption is at fast corner. Later, there are alternative powers at the alternative corners position, in dynamic power powers which remain constant across different corners. When the increase in the supply voltage specially in the cornors the leakage voltage gradually significant. From the same algorithm, for different key size there is a minor differences of power leakage. The PROPOSED module of leakage power is 1/3 times of leakage power of a AES module. From dynamic power, since our system is optimization by using separated clock gating for different key size for the different configuration, the AES module with 128-bit key optain upto 22% less dynamic power than the AES moduke for 192-bit and 256-bit key size with a smaller margin. The decrease in the supply voltage returns decreses power consumptoion gradually. From the satisfactory case of our energy intake is at zero.6 V and the leakage from the one-of-a-kind key configuration for two algorithms is closer to every different. At regular corner for the deliver voltage of 0.6 V, the worst case energy consumption is (at  $150^{\circ}$  C), wherein AES module consumes the power usage from 61.5 to 65.6  $\mu$ W in total and from the PROPOSED module consumes the power utilization of handiest 24  $\mu$ W; from the everyday case at 50C, our AES module and our PROPOSED module consumes best less than 20 and 12  $\mu$ W, respectively.

Moreover from, [11] where the estimation of energy consumption per bit of two designs. From the proposed work we can achieve the extreme low energy per bit is 0.6 V. In typical case for 50 \_C, our proposed AES module for 128-bit, 192- bit and 256-bit keys, 0.65, 0.78, and 0.81 pJ/b is achieved, respectively. From SNACk test chip, for 128-bit key AES needs forty five cycles calls for to complete one encryption, for 192-bit key AES and 256-bit key AES needs 53 cycles and 61 cycles respectively. Lightweight algorithm PROPOSED which consumes the identical amount of energy according to bit and for AES the PROPOSED needs 74 cycles to do encryption of 128-bit records block in 128-bit key mode. From the worst case at 150°C, our AES consumes much less than 3 pJ/b, whilst from proposed desires only less than 2 pJ/b.

Our proposed work is compared with the state of the art as shown in IV-C and from IV-B. From AES module in proposed system with only 128-bit key is 1.65 times higher comapred with other same technology node. Moreover, our system has 4 times more throughput based on the design of RSA and 8 times more throughput based on the design od DES at the same operating frequency. The proposed system is comparied with the same 32-bit datapath, and according to our optimization, we achieved more than 20% improvement in the power consumption from TSMC 65 nm which compared with different work with a small increment in terms of gate counts. Our system consumes at the least power of (20  $\mu$ W at 0.6 V) when it is compared with the 8-bit datapath design with same throughput of 30 Mb/s.Our proposed device is 3 instances lesser strength intake than in the 8-bit datapath design for low electricity and coffee energy. In case of energy performance, our design consumes very much less energy per bit among the lowcost design structure with 0.65 pJ/b (at 0.6 V, 50°C); the energy consistent with bit for the high-overall performance design in (0.511 pJ/b at 409  $\mu$ W, 0.34 V).

# C. Security Evaluation

Our proposed is tested with a correlation energy evaluation (CPA) attack, that's one of the maximum used effective side channel attacks, on the premise of our design using the least spherical key hypothesis. The simulation of 25000 encryptions from our layout with 128-bit key encryption is accomplished which is to capture the ciphertext and the power strains. For the assessment, the equal hardware implementation process and the overall parallel layout from OpenCores. For extra parallel degree inside the datapath, the hard is to

assemble parallelism is one of the way of hiding counter measures. The 8-bit datapath with out the protection is more outrated and this sort of assault is used because it calls for much less wide variety of lines to attack. Fig. 13 shows the outcomes of our proposed work on put up signal-off energy strains. The AES of 128-bit datapath desires 4000 strains to show is 16- little bit of the screat key, at the same time as our system even with 25000 strains, only calls for 12-bit are found out. Four bytes are hidden because at the stop of every round, the facts registers are overridden with new records. This hides the correlation of the hobby of the ultimate 4 B of the key which increase the resistance of our layout to the closing round CPA.

TABLE I

UNITS FOR MAGNETIC PROPERTIES

| Symbol                        | Quantity                                     | Conversion from Gaussian and CGS EMU to SI <sup>a</sup>                                                                       |

|-------------------------------|----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| Φ                             | magnetic flux                                | $1 \text{ Mx} \rightarrow 10^{-8} \text{ Wb} = 10^{-8} \text{ V} \cdot \text{s}$                                              |

| В                             | magnetic flux density,<br>magnetic induction | $1 \text{ G} \rightarrow 10^{-4} \text{ T} = 10^{-4} \text{ Wb/m}^2$                                                          |

| H                             | magnetic field strength                      | 1 Oe $\to 10^3/(4\pi)$ A/m                                                                                                    |

| m                             | magnetic moment                              | 1  erg/G = 1  emu                                                                                                             |

|                               |                                              | $\rightarrow 10^{-3} \text{ A} \cdot \text{m}^2 = 10^{-3} \text{ J/T}$                                                        |

| M                             | magnetization                                | $1 \text{ erg/}(G \cdot \text{cm}^3) = 1 \text{ emu/cm}^3$                                                                    |

|                               |                                              | $\rightarrow 10^3 \text{ A/m}$                                                                                                |

| $4\pi M$                      | magnetization                                | $1 \text{ G} \rightarrow 10^3/(4\pi) \text{ A/m}$                                                                             |

| σ                             | specific magnetization                       | $1 \operatorname{erg}/(G \cdot g) = 1 \operatorname{emu/g} \to 1 \operatorname{A} \cdot \operatorname{m}^2/\operatorname{kg}$ |

| j                             | magnetic dipole                              | 1  erg/G = 1  emu                                                                                                             |

|                               | moment                                       | $\rightarrow 4\pi \times 10^{-10} \text{ Wb} \cdot \text{m}$                                                                  |

| J                             | magnetic polarization                        | $1 \text{ erg/(G} \cdot \text{cm}^3) = 1 \text{ emu/cm}^3$                                                                    |

|                               |                                              | $\rightarrow 4\pi \times 10^{-4} \text{ T}$                                                                                   |

| χ,κ                           | susceptibility                               | $1 \rightarrow 4\pi$                                                                                                          |

| $\chi_{\scriptscriptstyle P}$ | mass susceptibility                          | $1 \text{ cm}^3/\text{g} \rightarrow 4\pi \times 10^{-3} \text{ m}^3/\text{kg}$                                               |

| μ                             | permeability                                 | $1 \rightarrow 4\pi \times 10^{-7} \text{ H/m}$                                                                               |

|                               |                                              | $=4\pi\times 10^{-7} \text{ Wb/(A·m)}$                                                                                        |

| $\mu_{\rm r}$                 | relative permeability                        | $\mu \rightarrow \mu_r$                                                                                                       |

| w, W                          | energy density                               | $1 \text{ erg/cm}^3 \rightarrow 10^{-1} \text{ J/m}^3$                                                                        |

| N, D                          | demagnetizing factor                         | $1 \to 1/(4\pi)$                                                                                                              |

Vertical lines are optional in tables. Statements that serve as captions for the entire table do not need footnote letters.

### V. CONCLUSION

In the presented article, The proposed work offered modified strategies optimization for optimization using AES 32-bit datapath with hierarchical levels of safety. Our proposed structure is pointed through a identification of key increment and data path which minimize the effect on control statement and registers. The machine electricity intake is decreased by way of deciding on the proper S-box containers for decrease power any decreasing the activities of the datapath and key expansion with the aid of using clock gating approach for the information garage. The throughput is increased via using 8 S-boxes containers and constructing key exposure in parallel with encryption path. AES multiple key sizes for the encryption module gives specific protection stages which assist the actual-time IoT packages and can used to a much broader variety of safety protocols and mechanisms. From the results, our optimization strategies is not just useful for area, energy/electricity consumption, and throughput however also the safety attributes. By Comparing, our modified AES technique with available AES technique has showed optimized energy consumption compared to existing security techniques.

$<sup>^{</sup>a}$ Gaussian units are the same as cg emu for magnetostatics; Mx = maxwell, G = gauss, Oe = oersted; Wb = weber, V = volt, S = second, T = tesla, M = meter, A = ampere, M = berry.

## REFERENCES

- [1] C. Srinivasan, B. Rajesh, P. Saikalyan, K. Premsagar, and E. S. Yadav, "A review on the different types of internet of things (iot)," Journal of Advanced Research in Dynamical and Control Systems, vol. 11, no. 1, pp. 154–158, 2019.

- [2] L. Xu and N. Pombo, "Human behavior prediction though noninvasive and privacy-preserving internet of things (iot) assisted monitoring," in 2019 IEEE 5th World Forum on Internet of Things (WF-IoT). IEEE, 2019, pp. 773–777.

- [3] B. Maram, J. Gnanasekar, G. Manogaran, and M. Balaanand, "Intelligent security algorithm for unicode data privacy and security in iot," Service Oriented Computing and Applications, vol. 13, no. 1, pp. 3–15, 2019.

- [4] D. Serpanos and M. Wolf, "Security testing iot systems," in Internet-of-Things (IoT) Systems. Springer, 2018, pp. 77–89.

- [5] P. Fishburn, "Additive utilities with incomplete product set: Applications to priorities and," 1967.

- [6] B. N. Silva, M. Khan, and K. Han, "Internet of things: A comprehensive review of enabling technologies, architecture, and challenges," IETE Technical review, vol. 35, no. 2, pp. 205–220, 2018.

- [7] T. Qiu, N. Chen, K. Li, M. Atiquzzaman, and W. Zhao, "How can heterogeneous internet of things build our future: A survey," IEEE Communications Surveys & Tutorials, vol. 20, no. 3, pp. 2011–2027, 2018.

- [8] V. P. Nikshepa and U. K. K. Shenoy, "6lowpan—performance analysis on low power networks," in International Conference on Computer Networks and Communication Technologies: ICCNCT 2018, vol. 15. Springer, 2018, p. 145.

- [9] Z. Yang and C. H. Chang, "6lowpan overview and implementations," in Proceedings of the 2019 International Conference on Embedded Wireless Systems and Networks. Junction Publishing, 2019, pp. 357–361.

- [10] B. Peres, B. P. Santos, A. d. O. Otavio, O. Goussevskaia, M. A. Vieira, L. F. Vieira, and A. A. Loureiro, "Matrix: Multihop address allocation and dynamic any-to-any routing for 6lowpan," Computer Networks, vol. 140, pp. 28–40, 2018.

- [11] Y. Qiu and M. Ma, "Secure group mobility support for 6lowpan networks," IEEE Internet of Things Journal, vol. 5, no. 2, pp. 1131–1141, 2018.

- [12] M. A. Mahmud, A. Abdelgawad, and K. Yelamarthi, "Improved rpl for iot applications," in 2018 IEEE 61st International Midwest Symposium on Circuits and Systems (MWSCAS). IEEE, 2018, pp. 988–991.

- [13] R.-A. Koutsiamanis, G. Z. Papadopoulos, X. Fafoutis, J. M. Del Fiore, P. Thubert, and N. Montavont, "From best effort to deterministic packet delivery for wireless industrial iot networks," IEEE Transactions on Industrial Informatics, vol. 14, no. 10, pp. 4468–4480, 2018.

- [14] D. Li, Z. Cai, L. Deng, and X. Yao, "Iot complex communication architecture for smart cities based on soft computing models," Soft Computing, vol. 23, no. 8, pp. 2799–2812, 2019.

- [15] C. O. Chan, H. C. Lau, and Y. Fan, "Iot data acquisition in fashion retail application: Fuzzy logic approach," in 2018 International Conference on Artificial Intelligence and Big Data (ICAIBD). IEEE, 2018, pp. 52–56.

- [16] G. Sunitha, S. D. Kumar, and B. V. Kumar, "Energy balanced zone based routing protocol to mitigate

congestion in wireless sensor networks," Wireless Personal Communications, vol. 97, no. 2, pp. 2683–711, 2017.

[17] R. Hassan, A. M. Jubair, K. Azmi, and A. Bakar, "Adaptive congestion control mechanism in coap application protocol for internet of things (iot)," in 2016 International Conference on Signal Processing and Communication (ICSC). IEEE, 2016, pp. 121–125.